# FPGA IMPLEMENTATION OF DIGITIZED PHASE-LOCKED LOOP WITH TOLERANCE TO PVT VARIATIONS

#### D.Sridharan, Mrs.P.Meenakshi vidya

**Abstract**— A spread-spectrum clock generator (SSCG) is realized by an under-damping all-digital phase-locked loop (PLL). In this SSCG, the spread spectrum clocking is achieved by switching the divider without a delta-sigma modulator. By using a digital self-calibration technique, the frequency of this SSCG has a triangular modulation and relaxes the process variations. This SSCG is fabricated in a 0.18m CMOS process. The measured electro-magnetic interference reduction is 14.32dB. The measured rms and peak-to-peak jitters are 1.43ps and 13.31ps in a PLL mode, respectively. The measured rms and peak-to-peak jitters are 2.65 ps and 19.86ps in a spreadspectrum modulation, respectively.

Index Terms— Phase ed loop(PLL), Spread Spectrum Clock generator(SSCG), Convolutional coding, BCH coding, adaptive quantizers. lock

. \_ \_ \_ \_ \_ \_ \_ \_ \_ \_

#### **1** INTRODUCTION

A phase-locked loop or phase locked loop is a control system that generates an output signal whose phase is related to the phase of an input signal. While there are several differing types, it is easy to initially visualize as an electronic circuit consisting of variable а frequency oscillator and a phase detector. The oscillator generates a periodic signal[1]. The phase detector compares the phase of that signal with the phase of the input periodic signal and adjusts the oscillator to keep the phases matched. Bringing the output signal back toward the input signal for comparison is called a feedback loop since the output is 'fedback' toward the input forming a loop. Keeping the input and output phase in lock step also implies keeping the input and output frequencies the same. For all-digital methods, the matching requirements for the delay cells in the delay line limit the accuracy of the frequency modulation profile. The self-calibration will be also needed. A self-calibration circuit calibrates the SSCG in the background to relax the pressuress, voltage, and temperature (PVT) variations.

#### 2 BASICS OF PHASE LOCKED LOOP

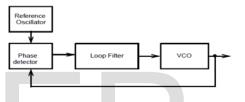

The Phase Locked Loop has three main blocks. It includes Phase detector, Loop filter and Voltage controlled oscillator as shown in fig.1. Phase detector compares between input and DCO output signal. Output depends upon the phase error. Output signal contains low frequency and higher frequency component. Loop filter is simply act as a integrator.

Figure 1. Basic layout of phase locked loop

Voltage Controlled Oscillator is treated as a linear, timeinvariant system. Excess phase of the VCO is the system output. Output frequency can be changed by changing the output of the loop filter.

#### 3 TYPES OF PLL

PLL includes five types. They are analog phase-locked loop also referred to as a linear phase-locked loop, digital phase-locked loop, all digital phase-locked loop, software phase-locked loop and Neuronal PLL.

#### A. Linear PLL:

The Analog or linear PLL has phase detector and loop filter. Phase detector is an analog multiplier. Loop filter is active or passive. Uses a Voltage-controlled oscillator.

#### B. Digital PLL:

Digital PLL is an analog PLL with a digital phase detector such as XOR, edge-trigger JK, phase frequency detector. May have digital divider in the loop.

#### C. All Digital PLL:

All digital PLL has Phase detector, filter and oscillator are digital. Uses a numerically controlled oscillator.

#### D. Software PLL:

Software PLL which includes functional blocks that are implemented by software rather than specialized hardware.

341

D.Sridharan is currently pursuing master's degree program in VLSI Design at Easwari

Engineering Collge. E-mail: kdsridharan@gmail.com

Mrs.P.Meenakshividyais currently working as Asst.Professor, ECE Department, Easwan Engineering College Ramapuram, Chennai-89. E-mail: meenakshividya.p@gmail.com

#### E. Neuronal PLL:

Neuronal PLL has an Phase detector, filter and oscillator are neurons or small neuronal pools. Uses a rate controlled oscillator .

In this ,All Digital Phase Locked Loop is discussed detailed.

#### 4 ALL DIGITAL PHASE LOCKED LOOP

The All-digital phase locked loop (ADPLL) is a phase lock loop implemented in purely digital circuitry and operating on finite precision digital words. ADPLL has an operating input frequency between 10 kHz to 150 kHz.

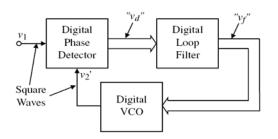

Figure.2. Basic Block Diagram of ADPLL

Output frequency between 10MHz to 300 MHz. Block diagram for All Digital Phase Locked Loop (ADPLL) is shown in Fig.2. ADPLL benefits are digital design regarding area, power consumption, and flexibility. Components of ADPLL includes Digital Phase Detector, Digital loop filter and Digitally Controlled Oscillator.

#### **A.Digital Phase Detector:**

The phase frequency detector is a significant aspect of the PLL because it determines whether the reference clock and divided DCO clock are in phase and are running at the same frequency. A modified D Flip-flop was utilized because the D input doesn't change and remains high always. The output of the modified D Flip-flops enters a two input NOR gate that resets the Flip-flops if both clocks are high. The up and down signals indicate if the DCO clock needs to be increased (up is true) or decreased (down is true). The event and direction signal are necessary to create the up and down enable signals for the T2D converter. Additional circuitry between the PFD and T2D is required for the signal conversion to takes place.

#### **B.Digital Loop Filter:**

Digital loop filter simplest loop filter. It is always operate in conjunction with EXOR or JK FF phase detector. For getting clock and direction signal a pulse forming circuit is used. Counter is incremented on each UP pulses and it is decremented on each down signals .So counter adds both pulses .So its work like an integrator. Loop filter has has two counters .Both are independent .One is called Up and other is Down counter .But both counts in upward direction. Counter has modulus k. So counter contents has range from 0 to k-1.Couter clock frequency is M times multiple of center frequency. M has typical values of 8, 16, 32....Down counter is enabled when DN/UP has logic high and up counter is enabled when this logic low value. When contents exceed k-1 both counters resets. "Carry" is MSB of the Up counter .The "borrow" signal is MSB of the Down counter. When Up-counter stored data  $\geq k/2$  "carry" is high .When down counter stored data $\geq k/2$  "borrow" is high. Frequency of DCO is controlled by positive edges of the signal.

#### C.Digitally Controlled Oscillator:

Digitally Controlled oscillators are nothing but a modified oscillator. Depending upon output of the loop filter they change their frequency. Divide by N counter DCO and Increment-decrement counter are the types of DCO. A simple÷N counter works as DCO. High frequency signal operates at very high frequency. Divide by N counter produces N bit parallel output. Drawback is that it can't design jitter. Increment-Decrement Counter consists of two blocks. Carry is assigned to DECR input and Borrow is assigned to INCR input. ID counter with ÷ N counter for again dividing the OUT. Clock of increment-decrement counter is 2N times multiple of center frequency.

TABLE I COMPARISON OF ANALOG AND DIGITAL PLL

| Parameter             | Digital PLL               | Analog PLL |

|-----------------------|---------------------------|------------|

| Power                 | 5.883 dBm                 | 3.5 dBm    |

| Lock time             | 1.5us(100-<br>120 cycles) | 10us       |

| Jitter/Phase<br>Noise | 0.4ns                     | -212dBc/Hz |

# **5 JITTER**

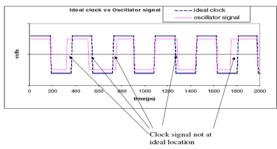

Jitter is the undesired deviation from true periodicity of anassumedperiic signal in electronics and telecommunications often in relation to a reference clock source. Jitter may be observed in characteristics such as the frequency of successive pulses, the signal amplitude, or phase of periodic signals. Jitter is a significant, and usually undesired, factor in the design almost all communications links of (e.g., USB, PCIe, SATA, OC-48). In clock recovery applications it is called timing jitter. Jitter can be quantified in the same terms as all time-varying signals, e.g., RMS, or peak-to-peak displacement. Also like other time-varying signals, jitter can be expressed in terms of spectral density (frequency content). The waveform for Jitter is shown in figure 3. Jitter period is the interval between two times of maximum effect (or minimum effect) of a signal characteristic that varies regularly with time[3]. Jitter frequency, the more commonly quoted figure, is its inverse. ITU-T G.810classifies jitter frequencies below 10 Hz as wander and frequencies at or above 10 Hz as jitter.

Figure.3. Example of jitter

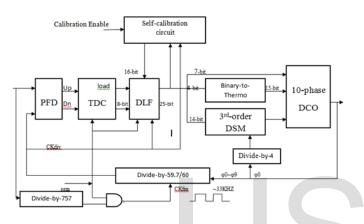

Figure.4. Proposed DPLL with PVT variations.

# Frequency Dual-Modulus Divider:

In order to realize a factional division ratio of 59.7, a 10-phase DCO is adopted in this work. The factional dualmodulus divider, which is realized by a divide by (N-1/10)/(N+1/5) divider, a program counter, a swallow counter, and auxiliary digital circuits. When SSM=0,this ADPLL works in a PLL mode and S=4 is selected. When S is equal to 4,the division ratio is 60. The clock is 33KHZ switches values between three and four respectively. This time interval is equal to 200 p for the DCO of 1.5 GHz. Because of this large timing margin of 200 ps, the 10-1 MUX can be realized by conventional static logics.Both are independent .One is called Up and other is Down counter .But both counts .in upward direction. Counter has modulus k. So counter contents has range from 0 to k-1.Couter clock frequency is M times multiple of center frequency. M has typical values of 8, 16, 32....Down counter is enabled when DN/UP has logic high and up counter is enabled when this logic low value. When contents exceed k-1 both counters resets.

# **Digital Self-Calibration Circuit:**

The variations not only affect the down-spreading ratio and triangular modulation profile, but also the loop bandwidth, EMI reduction and jitter performance. Three process corners are considered for NMOS and PMOS devices, fastfast (FF) corner with 0'c, typical-typical (TT) corner with 27'c,

and slow-slow (SS) corner with 80'c. According to simulation results, the simulated parameters Kc and TDC for these three corners are listed. To tolerate the PVT variations, the nature frequency and damping factor should be adjusted. In this work, the proportional and integral gains, Kp and Ki, of the DLF are adjusted by a digital self-calibration circuit to achieve the required the nature frequency and damping factor. The spread spectrum ratio of 5000 ppm. The required Kp and Ki for FF, TT and SS corners are 448 and 2, 1024 and 5 2432 and 13, respectively.

TABLE II COMPARISON OF SYNTHESIS RESULTS

| Technique                     | Pressure | Volume | Temperature |

|-------------------------------|----------|--------|-------------|

| 1 <sup>st</sup> -order<br>DSM | 23.4 mW  | 33KHz  | 1.5GHz      |

| 3 <sup>rd</sup> -order<br>DSM | 20 mW    | 25KHz  | 1GHz        |

### 6 CONCLUSION

A triangular-wave-modulation SSCGis realized by switching the divider of an ADPLL without a DSM. To reduce the phase jumping step, a 10-phase DCO and a fractional divider are adopted.

Furthermore, the proposed system will be developed using verilog-HDL and FPGA implementation using a self-calibration circuit is also adopted to calibrate the SSCG in the back-ground to tolerate the PVT variations. This chip has been fabricated a 0.12 m CMOS process.

# REFERENCES

- [1] H.W. Chen and J. C.Wu, "A spread-spectrum clock generator for EMI reduction," *IEICE Trans. Electron.*, pp. 1959–1966, Dec. 2001.

- [2] H.-H. Chang, I.-H. Hua, and S.-I. Liu, "A spread spectrum clock generator with triangular modulation," *IEEE J. Solid-State Circuits*, vol.

38, no. 4, pp. 673–677, Apr. 2003.

- [3] H.-R. Lee, O. Kim, G. Ahn, and D.-K. Jeong, "A low-jitter 5000 ppm spread spectrum clock generator for multi-channel SATA transceiver in 0.18 CMOS," in Proc. IEEE Int. Solid-State Circuit Conf. Dig. *Tech. Papers*, Feb. 2005, pp. 162–163.

- [4] M. Kokubo, T. Kawamoto, T. Oshima, T. Noto, M. Suzuki, S. Suzuki, T. Hayasaka, T. Takahashi, and J. Kasai, "Spread-spectrum clock generator for serial ATA using fractional PLL controlled by modulator with level shifter," in Proc. IEEE Int. Solid-State Circuit Conf.*Dig. Tech. Papers*, Feb. 2005, pp. 160–161.

- [5] D.-S. Shen and S.-I. Liu, "A low-jitter spread spectrum clock generator

using FDMP," IEEE Trans. Circuits Syst. II, Exp, Briefs, vol. 54, pp. 979–983, Nov. 2007.

S.-Y. Lin and S.-I. Liu, "A 1.5 GHz all-digital spread-spectrum clock generator," *IEEE J. Solid-State Circuits*, vol. 44, no. 11, pp. 3111– 3119, Nov. 2009. International Journal of Scientific & Engineering Research, Volume 6, Issue 4, April-2015 ISSN 2229-5518

- [7] S. Hwang, M. Song, Y.-H. Kwak, I. Jung, and C. Kim, "A 3.5-GHz spread-spectrum clock generator with a memoryless Newton-Raphson modulation profile," *IEEE J. Solid-State Circuits*, vol. 47, no. 5, pp. 1199–1208, May 2012.

- [8] I-Ting Lee, Shih-Han Ku, and Shen-Iuan Liu," An All-Digital Spread-Spectrum Clock Generator With Self-Calibrated Bandwidth", IEEE transactions on circuits and systems—i: vol. 60, no. 11, november 2013.

- [9] D. D. Caro, C. A. Romani, N. Petra, A. G. M. Strollo, and C. Parrella, "A 1.27 GHz, all-digital spread spectrum clock generator/synthesizer in 65 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 45, no. 5, pp. 1048–1060, May 2010.

- [10] SV. Kratyuk, P. K. Hanumolu, U. Moon, and K. Mayaram, "A design procedure for all-digital phase-locked loops based on a charge-pump phase-locked-loop analogy," IEEE Trans. Circuits Syst. II, Exp, Briefs,

vol. 54, no. 5, pp. 247-251, Mar. 2007.

# IJSER